Servicios integrales de fabricación electrónica que le ayudan a lograr fácilmente sus productos electrónicos de PCB y PCBA

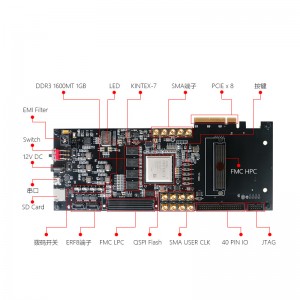

FPGA Xilinx K7 Kintex7 PCIe comunicación por fibra óptica

- DDR3 SDRAM: bus DDR3 de 64 bits de 16 GB, velocidad de datos de 1600 Mbps

- QSPI Flash: una pieza de QSPIFLASH de 128 mbit, que se puede utilizar para archivos de configuración de FPGA y almacenamiento de datos de usuario

- Interfaz PCLEX8: La interfaz estándar PCLEX8 se utiliza para la comunicación PCIE de la placa base del ordenador. Es compatible con el estándar PCI Express 2.0. La velocidad de comunicación monocanal puede alcanzar hasta 5 Gbps.

- Puerto serie USB UART: Un puerto serie, se conecta al PC a través del cable miniusb para realizar la comunicación serie

- Tarjeta Micro SD: la tarjeta Micro SD se inserta completamente, puede conectar la tarjeta Micro SD estándar

- Sensor de temperatura: un chip sensor de temperatura LM75, que puede monitorear la temperatura ambiental alrededor de la placa de desarrollo

- Puerto de extensión FMC: un FMC HPC y un FMCLPC, que pueden ser compatibles con varias tarjetas de expansión estándar

- Terminal de conexión de alta velocidad ERF8: 2 puertos ERF8, que admiten transmisión de señal de ultra alta velocidad Extensión de 40 pines: reservada una interfaz de E/S de extensión general con 2,54 mm40 pines, O efectivo tiene 17 pares, admite 3,3 V

- La conexión periférica del nivel y el nivel de 5 V pueden conectar los periféricos de diferentes interfaces 1O de propósito general.

- Terminal SMA; 13 cabezales SMA chapados en oro de alta calidad, lo que resulta conveniente para que los usuarios cooperen con tarjetas de expansión AD/DA FMC de alta velocidad para la recopilación y procesamiento de señales

- Gestión de reloj: Fuente de reloj múltiple. Incluye la fuente de reloj diferencial del sistema de 200 MHz SIT9102.

- Oscilante de cristal diferencial: cristal de 50 MHz y chip de gestión de reloj programable SI5338P: también equipado con

- EMCCLK de 66 MHz. Se adapta con precisión a diferentes frecuencias de reloj.

- Puerto JTAG: 10 puntos Puerto JTAG estándar de 2,54 mm, para descarga y depuración de programas FPGA

- Chip de monitoreo de voltaje de sub-reinicio: una pieza del chip de monitoreo de voltaje ADM706R, y el botón con el botón proporciona una señal de reinicio global para el sistema

- LED: 11 luces LED, indican la fuente de alimentación de la tarjeta de la placa, señal config_done, FMC

- Señal indicadora de encendido y 4 LED de usuario

- Tecla e interruptor: 6 teclas y 4 interruptores son botones de reinicio FPGA,

- El botón del programa B y 4 teclas de usuario están compuestos por 4 interruptores de doble tiro de una sola cuchilla.

Escribe tu mensaje aquí y envíanoslo

Categorías de productos

-

Teléfono

-

Correo electrónico

-

WhatsApp

-

Skype

-

Skype

-

Skype